SLUSFF6 April 2025 LMG1020-Q1

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

封裝選項

請參考 PDF 數(shù)據(jù)表獲取器件具體的封裝圖。

機械數(shù)據(jù) (封裝 | 引腳)

- YBV|6

散熱焊盤機械數(shù)據(jù) (封裝 | 引腳)

訂購信息

7.4.2 Layout Example

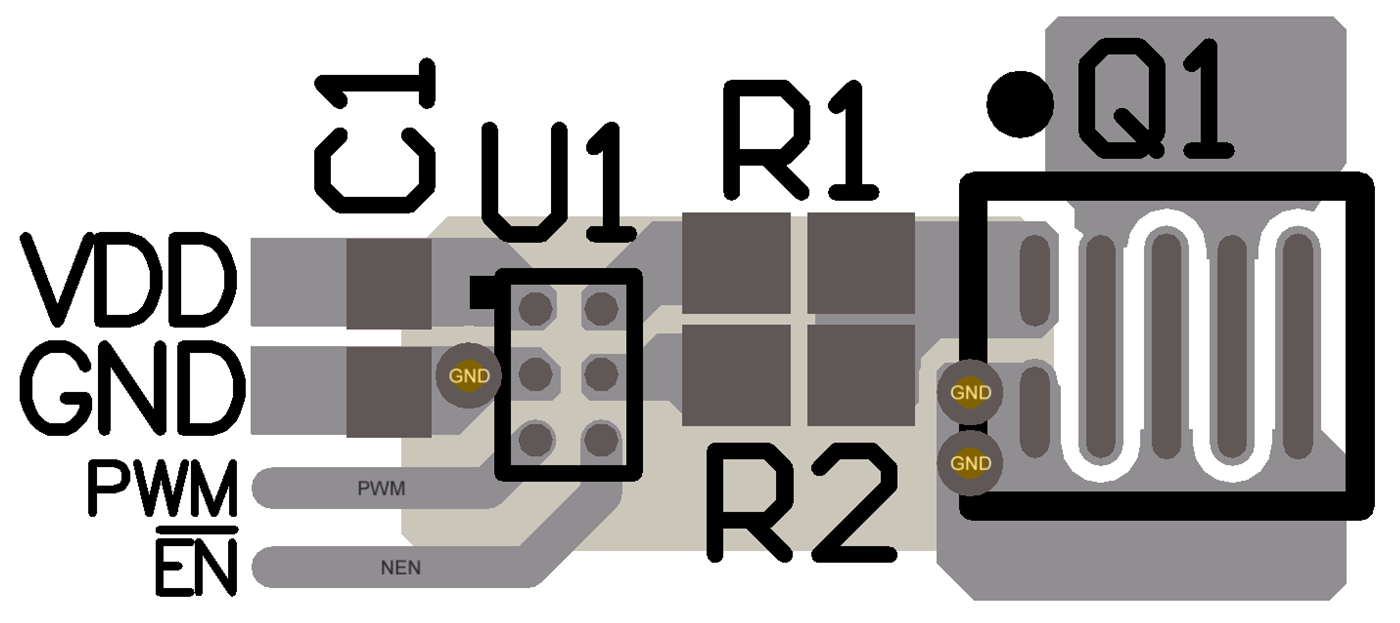

Figure 7-10 presents a typical layout of LMG1020-Q1 with a 0402 decoupling capacitor C1, which is placed as close as possible to LMG1020-Q1. The ground return at GaN FET Kelvin source immediately flows through a via to the closest inner layer, and overlaps with the top layer traces.

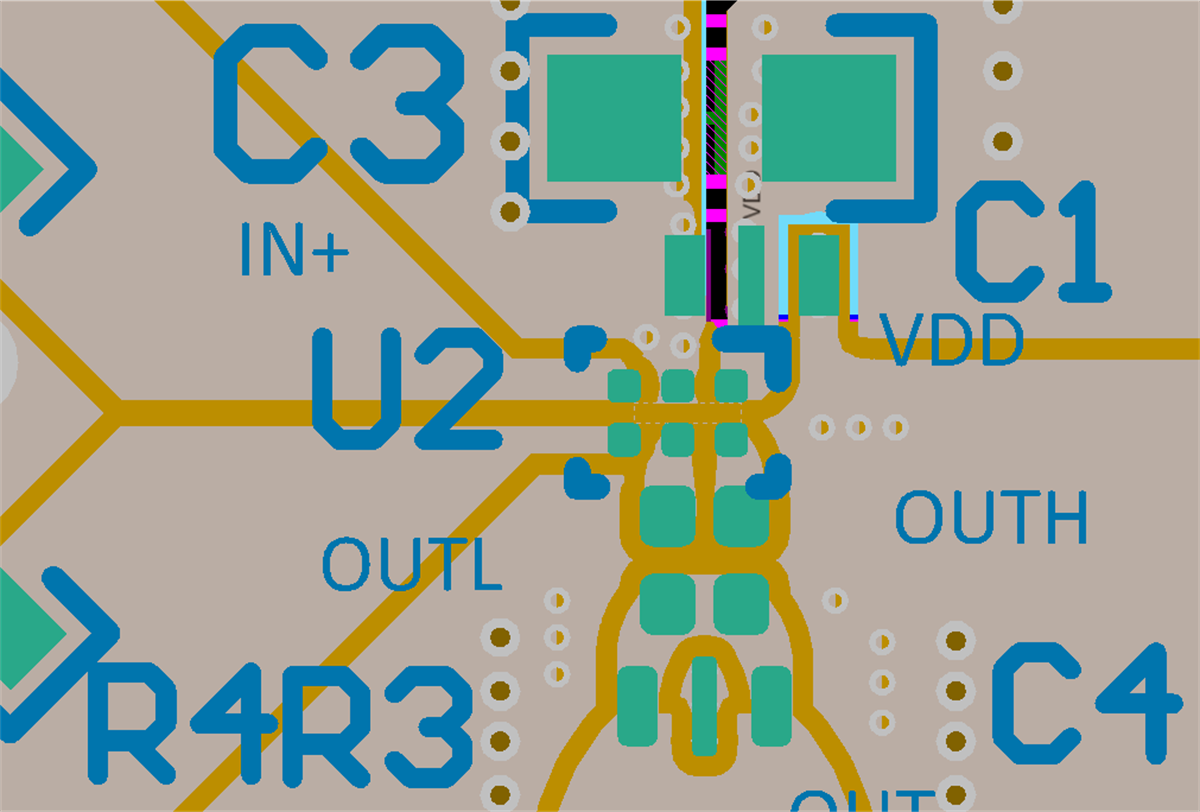

Figure 7-11 presents a layout of LMG1020-Q1 with a 0.1μF feed-through capacitor (C1) and a larger 1μF capacitor (C3) for decoupling. In this design, the feed-through capacitor C1 is placed in a shunt-through manner for lower noise decoupling, and C3 is placed next to C1. 0201 resistors are used at the output of LMG1020-Q1, which brings lower parasitic inductance than 0402 package.

Figure 7-10 Typical LMG1020-Q1 Layout

With Ball-Grid GaN FET And 0402 Decoupling

Capacitor

Figure 7-10 Typical LMG1020-Q1 Layout

With Ball-Grid GaN FET And 0402 Decoupling

Capacitor Figure 7-11 Typical Layout Of LMG1020-Q1 And A

Feed-Through Decoupling Capacitor With A Capacitor

Load

Figure 7-11 Typical Layout Of LMG1020-Q1 And A

Feed-Through Decoupling Capacitor With A Capacitor

Load